逐次比较型(A/D)转换器电路结构及工作原理

时间:2023-03-13 | 来源:佚名

|

1.转换方式

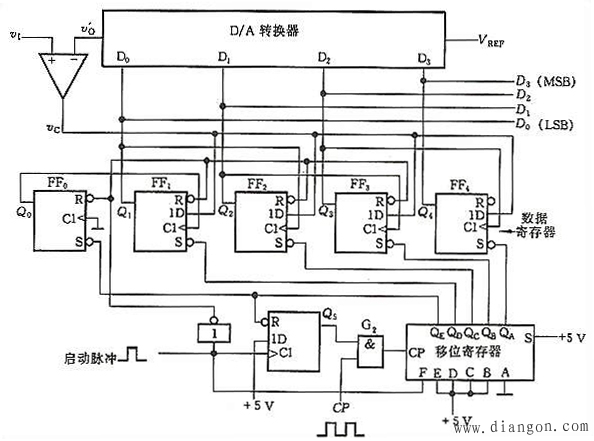

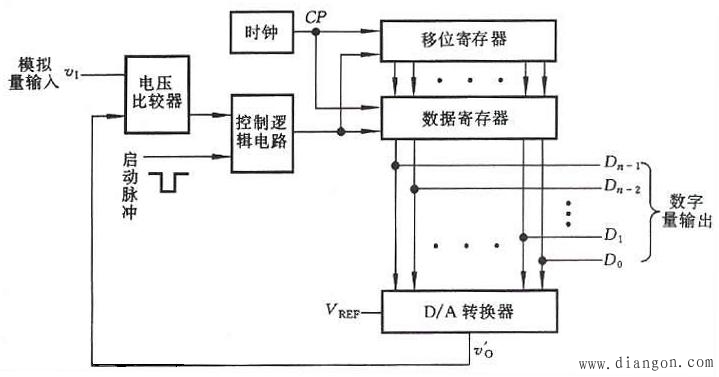

直接转换ADC 2.电路结构 逐次逼近ADC包括n位逐次比较型A/D转换器如图1所示。它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。  图1逐次比较型A/D转换器框图

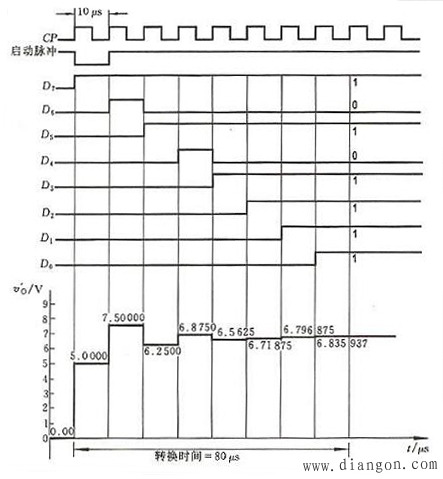

3.工作原理 逐次逼近转换过程和用天平称物重非常相似。天平称重物过程是,从最重的砝码开始试放,与被称物体进行比较,若物体重于砝码,则该砝码保留,否则移去。再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。照此一直加到最小一个砝码为止。将所有留下的砝码重量相加,就得此物体的重量。仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。 对1的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。输入电压首先与D/A转换器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI< VREF/2,则为0。比较结果存于数据寄存器的Dn-1位。然后在第二个CP作用下,移位寄存器的次高位置1,其他低位置0。如最高位已存1,则此时 vO'=(3/4)VREF。于是v1再与(3/4)VREF相比较,如v1≥(3/4)VREF,则次高位Dn-2存1,否则Dn-2=0;如最高位为0,则vO'=VREF/4,与vO'比较,如v1≥VREF/4,则 Dn-2位存1,否则存0……。以此类推,逐次比较得到输出数字量。

4.特点

(1)转换速度:(n 1)Tcp.速度快。 (2)调整VREF,可改变其动态范围。 5.转换器电路举例 图3 4位逐次比较型A/D转换器的逻辑电路

声明:本文转载自网络,不代表本平台立场,仅供读者参考,著作权属归原创者所有。我们分享此文出于传播更多资讯之目的。如有侵权,请联系我们进行删除,谢谢!

|