CD74HC74M96正品触发器电气功能设备参数信息

|

CD74HC74M96器件包含两个具有异步预设和清零引脚的,独立D类正边沿触发触发器,平衡的输出允许设备吸收和产生类似的电流,此设备的驱动能力可能在轻负载中创建快速边缘,应该考虑路由和负载条件以防止振铃。 此外,该器件的输出能够驱动比不使用该器件所能维持的电流更大的电流被损坏,重要的是要限制设备的输出功率,以避免过电流造成的损坏。CD74HC74可以驱动总电容小于或等于节6.6连接到高阻抗CMOS输入,同时仍然满足所有数据表规范,更大的可以施加电容性负载,但是不建议超过所提供的负载值。

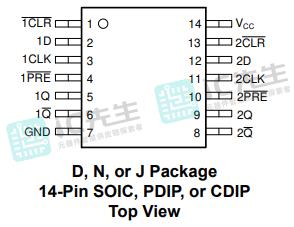

CD74HC74M96触发器的产品特性: 缓冲输入 宽工作电压范围:2V 至 6V 宽工作温度范围:-55°C 至 125°C 支持多达 10 个 LSTTL 负载的扇出 与 LSTTL 逻辑 IC 相比,可显著降低功耗 CD74HC74M96触发器的详细设计程序: 1、增加一个从VCC到GND的去耦电容器,电容器需要放置在物理上靠近器件,并且电接近VCC和GND引脚。 2、确保输出处的电容负载≤70 pF,这不是一个硬性限制,但它将确保最佳表演这可以通过从CD74HC74提供短的、适当尺寸的迹线来实现到接收设备。 3、确保输出处的电阻负载大于Ω,大多数CMOS输入具有电阻负载,测量单位为兆欧姆,远大于上面计算的最小值。 4、热问题很少是逻辑门关注的问题,但是功耗和热增加可以使用应用报告中提供的步骤、CMOS功耗和Cpd进行计算。 引脚功能图

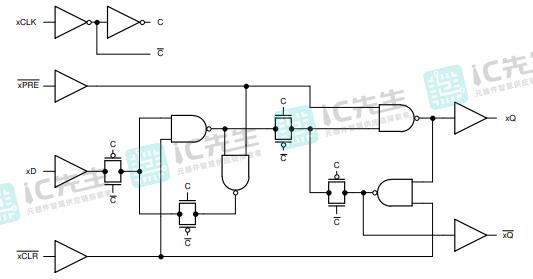

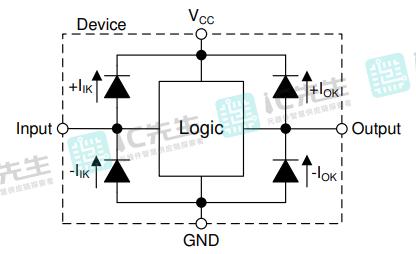

功能框图

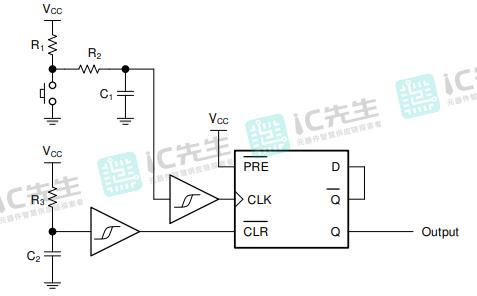

未使用的输入必须端接至VCC或接地,如果输入为完全未使用,或者如果要使用输入,它们可以与上拉或下拉电阻器连接有时,但并非总是如此,上拉电阻器用于HIGH的默认状态,下拉电阻器用于默认状态为LOW。 CD74HC74M96触发器具有标准CMOS输入,因此输入信号边缘速率不能很慢,输入边缘速率慢可能导致振荡和破坏击穿电流,电源可以是位于节 6.2.每个VCC端子应具有一个旁路电容器,以防止电源干扰。0.1μF电容器建议用于此设备,并联多个旁路帽以拒绝不同频率的噪音0.1μF和1μF电容器通常并联使用,旁路电容器应安装在尽可能靠近电源端子的位置,以获得最佳效果。 产品应用图

电气布置图

当使用多输入和多通道逻辑器件时,输入永远不能保持浮动,在许多数字逻辑器件的情况、功能或部分功能未被使用,例如,当使用三输入AND门,不能因为未定义的外部连接处的电压导致未定义的操作状态。 所有未使用的数字逻辑输入设备必须连接到由输入电压规范定义的逻辑高电压或逻辑低电压,以防止它们漂浮,必须应用于任何特定未使用输入的逻辑电平取决于设备的功能,通常,输入连接到GND或VCC,无论哪一个对逻辑更有意义功能或更方便。 |