小芯片:为什么是现在?

|

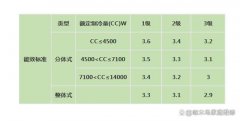

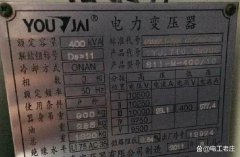

多芯片产品的想法已经存在了一段时间,目的是实现由更小的组件组成的更高功能的系统。例如,我们有 1980 年推出的大型机 CPU IBM 3081。它由多个芯片组成,分别封装并集成到更大的基板上. 然而,我们遇到的绝大多数处理器都是单片式的,处理器的所有功能都集中在一块硅片上。 随着处理器功能的不断扩展,其制造的复杂性也在增加。设计复杂性增长的速度,以及相应的制造能力的增长,被称为摩尔定律。如果不提及这个已有数十年历史的观察结果,就很难讨论最近对小芯片的兴奋。 好吧,在以他的名字命名的法律基础的同一篇论文中,戈登·摩尔 (Gordon Moore) 谈到了一项包含我们现在所知的小芯片的技术的演变:“它可能被证明更经济地构建由较小的功能组成的大型系统,这些功能是单独打包和互连的” 。 从每个解决方案的角度来看,你肯定知道设计公司选择追求小芯片设计作为其存在的主要原因。然而,我们看到许多因素已经达到了正确的条件,准备好采用不同于旧的整体式方法的方法。这些主要归结为芯片尺寸、前端晶圆加工成本、新节点上新设计的工程成本,以及封装解决方案的成熟度和精密度。 单片芯片尺寸 摩尔定律背后的创新引擎使得不断提高的设备集成水平可以继续适应相同的物理尺寸成为可能。例如,如果光刻缩小能够使构建块缩小 30%,那么可以在不增加裸片尺寸的情况下增加 42% 的电路。这大致是几十年来逻辑收缩的速度。然而,虽然逻辑倾向于很好地扩展,但并不是所有的半导体设备都享有这种优势,例如可以包含模拟电路的 I/O,扩展速度大约是逻辑的一半,对于台积电最近向 3nm 的过渡,SRAM 单元大小比例几乎没有。由于完整的 SOC 不仅需要逻辑门,还需要许多不同类型的设备电路,以及保持市场竞争力的最低水平创新,设计人员已经开始选择设计更大的单片芯片。较大管芯的危害在于对良率的影响,因为随着管芯变大,它包含足够多的关键缺陷从而导致其功能失调的可能性更高。 晶圆加工成本 光刻缩小并不便宜,因为改变晶体管的形状和尺寸只会伴随着更高价格的设备和更长的处理时间。因此,7nm 晶圆的成本高于 14nm 晶圆,5nm 晶圆的成本高于 7nm,依此类推……当我们在成本模型中检查这一趋势时,我们看到一个明显的趋势,即晶圆价格上涨,小芯片方法的经济性变得比单片更具吸引力。 前沿节点新设计的工程成本 每个新的芯片设计都需要设计和工程资源,并且由于新节点的复杂性不断增加,新设计的典型成本随着每个新工艺节点的增加而增加。这进一步激发了创建可重复使用的设计的动力。chiplet 设计理念使这成为可能,因为只需更改 chiplet 的数量和组合即可实现新产品配置,而不是启动新的整体设计。例如,通过将单个小芯片集成到 1、2、3 和 4 芯片配置中,可以通过一次流片创建 4 种不同的处理器品种。如果完全通过整体方法完成,这将需要 4 次单独的流片。 先进封装解决方案的成本和复杂性 这种不断增长的 chiplet 趋势的一个推动因素是 chiplet 相互连接方式的成熟。根据最终产品的功能,芯片到芯片互连需要支持高数据传输速度和低功耗。混合键合、硅桥、中介层和先进基板等技术正在使更多的芯片间通信成为可能。这些是 Yole Intelligence 的报告高端性能封装中详细讨论的技术种类. 随着这些技术的成熟,它们的实施成本变得更低,并进一步推动了不断增长的小芯片趋势。当然,整体解决方案的封装通常应该比等效的小芯片解决方案便宜。但是,当与 chiplet 的良率优势进行平衡时,我们看到了一种趋势,即随着 chiplet 封装成本溢价的下降,较小芯片尺寸的 chiplet 具有更好的经济性。

最后的想法 小芯片,一种已经存在了几十年的设计理念,现在正在找到它的时机。推动因素已达到临界水平,例如单片芯片尺寸需求和晶圆加工成本。促成因素开始趋于成熟,例如高性能封装解决方案。到目前为止,利用小芯片的主要参与者是世界上最大的半导体公司之一,并且已经通过内部方法、使用专有互连 IP 和组装来实现这一点。然而,随着 UCIe 和 OCP 的 Bunch-of-Wires 等互连标准受到关注,小公司为新生的小芯片生态系统做出贡献的进入壁垒将会减少。

|