高速电路设计中耦合电容的关键作用

|

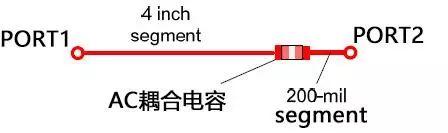

相对于需要进行复杂电路匹配的低频电路而言,高频电路的结构相对简单,但简单的结构往往意味着需要考虑更多的问题。以常见的AC耦合电容为例,要么在芯片之间加两颗直连,要么在芯片与连接器之间加两颗电容。尽管看起来简单,但在高速情况下一切都不同。高速使得这颗电容变得不够理想,如果这颗电容设计不好,可能会导致整个项目的失败。因此,对于高速电路而言,没有优化好这颗AC耦合电容将是致命的。 首先要明确AC耦合电容的作用。一般来说,我们使用AC耦合电容来提供直流偏压,即滤除信号的直流成分,使信号关于0轴对称。既然如此,那么这颗电容是否可以放置在通路的任何位置呢?这是我在刚开始涉足高频电路设计时遇到的第一个问题——AC耦合电容应该放在哪里。 让我们以一个常见的项目中经常遇到的典型通路进行分析。

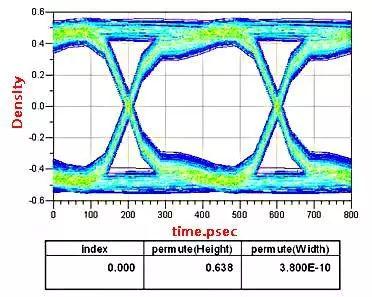

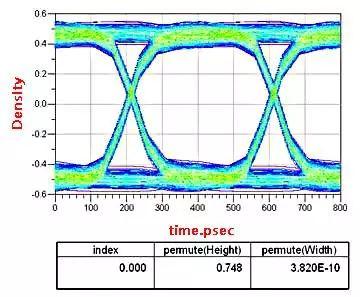

在低速电路设计中,这颗电容可以等效为理想电容。然而,在高频电路中,由于寄生电感和板材引起的阻抗不连续性的存在,实际上这颗电容不能被视为理想电容。在这个例子中,信号频率为2.5G,通道长度为4000mil,AC耦合电容的位置分别在距离发送端和接收端200mil的位置。让我们来看一下仿真得到的眼图变化。

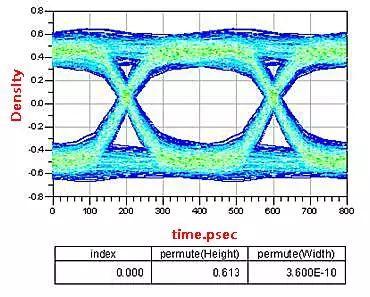

很明显,当AC耦合电容靠近接收端时,信号的完整性优于放置在发送端。我的理解是,由于非理想电容器的阻抗不连续性,信号经过通道衰减后反射的能量会小于直接反射的能量,因此大多数串行链路要求将AC耦合电容放置在接收端。然而也有例外,我之前在板对板连接时遇到过这个问题,查阅了PCIE规范后发现,如果是两个板之间的连接,通常将其放置在发送端,此时还能利用AC耦合电容的另一个作用——过压保护,例如SATA接口,因此通常要求靠近连接器放置。 解决了放置问题,另一个困扰大家的是容值的选择。换句话说,我们的整个串行链路等效为一个固定的电阻R,因此AC耦合电容C的选择将影响到时间常数(RC)。RC越大,直流分量越大,直流压降越低。那么AC耦合电容可以无限增大吗?显然是不行的。

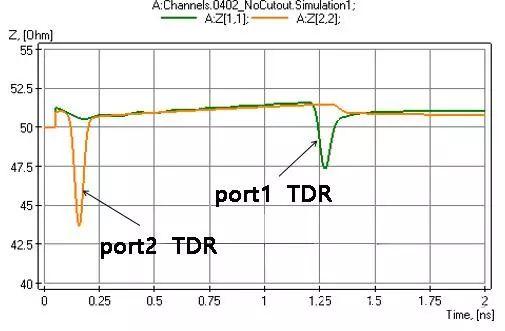

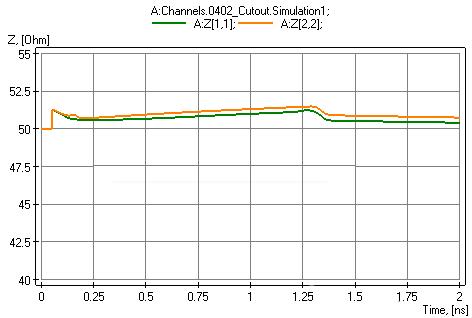

在同样的位置上,与图3进行比较,可以看到增大耦合电容后,眼图变窄。原因是高速使得电容变得不够理想。感应电感会引发串联谐振,容值越大,谐振频率越低,AC耦合电容在低频情况下呈感性,因此高频成分衰减加大,眼图变小,上升沿变缓,相应的抖动(JITTER)也会增加。通常建议AC耦合电容选择在0.01μF至0.2μF之间,而项目中常见的是0.1μF。推荐使用0402封装。 最后,在解决上述两个问题之后,从PCB设计的角度分析优化这颗电容。在实际项目中,与AC耦合电容的位置和容值这些明显的因素相比,更难把握的是板材本身(包括焊盘精度、铜箔均匀性等)以及焊盘处的寄生电容对信号完整性的影响。我们知道,高频信号必须沿着具有均匀特征阻抗的路径传播,如果遇到阻抗不匹配或不连续的情况,部分信号会反射回发射端,导致信号衰减,影响信号的完整性。在项目中,这种情况通常出现在焊盘或板载连接器处。在我最初涉足高速电路设计时,我经常遇到这个问题。 要解决这个问题,我们需要从两个方面着手。首先,在选择板材时,我们通常会选择高性能的ROGERS板材,因为ROGERS板材在控制铜箔厚度方面非常精确,均匀的铜箔覆盖大大降低了阻抗不连续性。其次,在消除焊盘处的寄生电容方面,行业常见的方法是在焊盘处进行隔层处理(挖空位于焊盘正下方的参考平面区域,在内层进行铜填充),通过增大焊盘与其参考平面(或返回路径)之间的距离,减小电容的不连续性。在我的项目中,使用介质均匀、铜箔宽度控制精确的ROGERS板材也有效提高了焊盘的加工精度。 通过仿真比较一下ROGERS板材进行精确隔层处理前后的信号完整性。

对比图5和图6,可以看出在未处理时阻抗有明显跃变,而进行隔层处理后,阻抗得到了显著改善,几乎没有任何跃变或不连续。

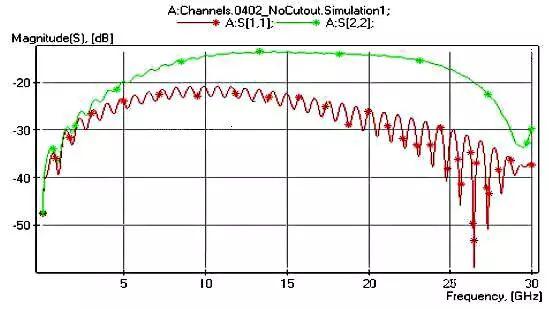

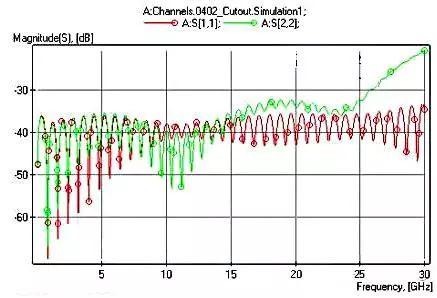

通过图7和图8的比较,可以看出,在使用ROGERS板材进行隔层处理后,与未进行隔层处理相比,回波损耗下降至-30dB以下,大大降低了回波损耗,确保了信号传输的完整性。 综上所述,要解决高频电路中这颗“致命”的AC耦合电容,不仅需要在电路设计上下功夫,同时选择性能更好的高频PCB板材也能事半功倍。 文章内容整理自网络,仅作为学习交流使用,如有侵权请联系沟通。 |