MLCC电容为什么要靠近电源引脚

|

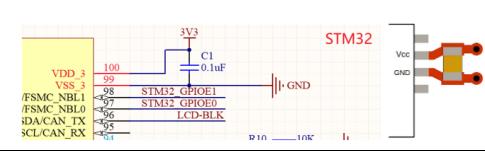

在硬件设计中,不论是电源芯片还是单片机芯片,有经验的工程师通常会在其周围放置一两个MLCC电容,通常采用100nF 10nF的电容组合,并紧密靠近芯片的电源引脚。

这样的做法可以改善电源纹波。关于这一点,一般的结论是,陶瓷电容距离芯片引脚越近,去耦效果越好,对滤除高频噪声也越有效。相比之下,将电解电容放置靠近芯片引脚效果不明显。对于“去耦半径”的术语,有些显得高深:当芯片对电流需求发生变化时,会在电源平面的一个非常局部的区域内产生电压扰动,电容必须补偿这一电流(或电压),因此必须先感知到这个电压扰动。电容能感知最大距离的电流/电压扰动的能力被称为去耦半径。这是根据资料找到的解释,尽管看过之后仍有些难以理解。因此,为了说明MLCC电容靠近或远离电源芯片引脚的影响有多大,我将通过实验来说明。 这种紧贴芯片引脚的电容称为退藕电容,与之对应的是耦合电容(couple cap)。退藕电容的名字可以理解为,它去除了不需要的耦合信号。我们可以通过仿真来观察电容对电源电压的影响。

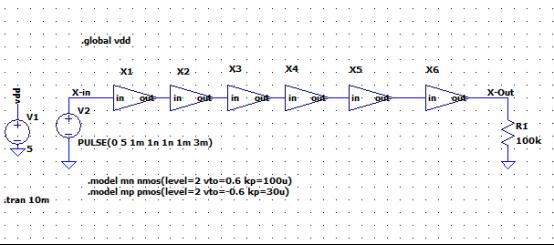

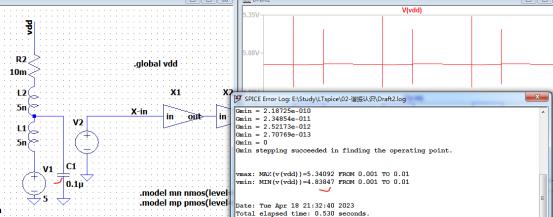

我进行了以下四个仿真测试实验:驱动信号控制反相器不停地翻转,接一个100K的负载,基本上产生了很小的电流,这种情况基本上相当于轻负载。在这种负载影响下,电源是否出现电压波动呢? 在仿真参数设计中,电源到反相器X1-X6的走线具有10nF的寄生电感和10mΩ的走线阻抗。使用的电容和电感模型均由仿真软件提供。当没有加电容时测量的结果显示,Vdd电源电压的最大和最小值在5.5V到4.7V之间,Vpp=0.7V。

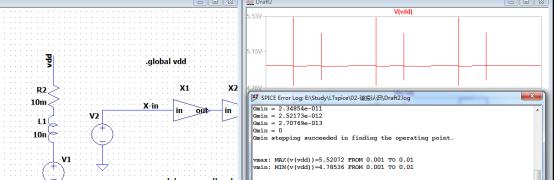

接着,在紧贴芯片电源引脚处放置一个MLCC电容进行仿真,Vdd纹波电压明显降低,峰峰值只有Vpp=0.1V。

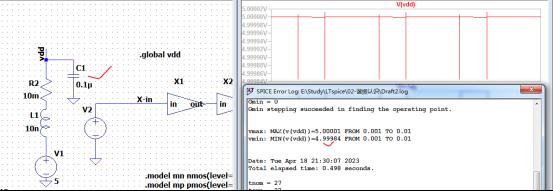

如果将MLCC电容放置稍远离电源引脚,仿真之后,Vdd纹波电压又增加了,变为最大和最小值在5.3V到4.8V之间,Vpp=0.6V。

通过这三个简单的仿真实验,可以看出,不论是多么轻载的情况下,由于走线的不可避免的寄生电感和等效阻抗的影响,都会造成电源电压的波动。使用MLCC电容后,可以在电源线上滤除负载波动时产生的高频波动。通常靠近芯片电源引脚的退耦电容可以理解为一个蓄能池,当负载芯片需要高速切换电流时,电容会迅速补偿电流引起的电压变化。假设此时芯片引脚没有MLCC电容,这个时候就需要从更远端的电源获取电流。由于距离越远,负载会在线路上的寄生电感和等效电阻作用下产生电压降甚至电压震荡。这也是为什么电解电容靠近芯片电源引脚,起不到和MLCC相同作用的原因。电解电容的ESR相对较大,而铝电解电容的ESL也大,因此电解电容同样无法快速响应高速负载电流切换需求。但是MLCC电容毕竟不是理想电容,也有阻抗曲线变化,因此在设计电路时,需要选择MLCC的谐振频率和电路的工作频率接近,这个时候MLCC电容的阻抗最低,在高速电流切换时,MLCC电容阻抗产生的噪声电压更小,也可以说滤波效果更好。因此,随着工作频率的升高,MLCC电容的退耦效果会逐渐变差,这是由于MLCC在高频时更趋向于表现出电感特性。因此,这时候需要并联更小容值的电容器,这也是为什么在DSP高速数字芯片的电源引脚上经常看到并联100nF 10nF 1nF 0.1pF的MLCC电容组合。然而,使用这种电容组合时,需要注意不同容值引起的反谐振问题。如果对电源噪声要求没有那么高,实际上也可以不使用这么多电容并联,毕竟增加电容数量也会增加成本。

文章内容整理自网络,仅作为学习交流使用,如有侵权请联系沟通。 |