25 kW SiC直流快充设计指南之PFC仿真

|

电源仿真有助于在设计和构建硬件系统之前验证假设,发现在器件选型、PCB layout、甚至后期测试中可能存在的问题。例如,仿真能帮助我们测试有关电压、电流、开关频率、损耗、散热和控制算法的工作。

除了验证,仿真的结果还有助于解决设计过程中其它重要的步骤,比如被动器件的选择。一套有效的仿真流程能够减少产品开发周期的调试以及硬件损耗,加快整个过程。

仿真之前的准备工作

在仿真开始之前,事前准备也是十分重要的。下面列出了我们认为最重要的几项准备工作,以及对应的处理方式。

仿真的目标

事前想好仿真目标是非常重要的。目标会影响建立仿真模型的细节,我们将会在下一部分中着重提到。在这个项目中,PFC的电源仿真帮助设计团队解决了以下几个问题:

电源仿真模型和软件

仿真模型是整个过程中的关键。模型再现了电路中每个器件的功能和参数。模型中的每个器件,比如:开关管、二极管、栅极驱动器以及被动器件,都可以用不同程度的参数增加细节。当然也存在难以建模的器件。一套复杂的模型运行起来会更加耗时,较简单的模型能够在许多不同系统条件下进行仿真,从而对应不同问题。

本次系统的开发捷径是简化模型,从而加速仿真和设计过程。当然,模型的精确性是非常关键的,会大大影响到结果。我们对不影响功能和电气参数的器件模型进行了简化处理,而对关键器件进行了更加精确的建模。

仿真软件

电源仿真常常基于已有的SPICE模型,在这个项目中,我们使用了SIMetrix,混合模式的仿真软件,为快速收敛提供强大的仿真功能。

输入参数

模拟的最后一个基本要素是评估那些特定器件和参数。这样的仿真能够帮助我们提供这些满足系统要求的参数的最佳组合。本次设计中,我们认为最重要的器件有:

1 PFC电感。PFC电感的参数应当尽早地根据应用的要求,输入电压,功率和电流确定。其次,我们应该考虑它的尺寸和性价比。设计团队计算并估计感值应该在几十μH以内。 2 输出电容。电容的选择基于回路电流和纹波电压,由于DC母线的电压较高(约1000 V),所以我们需要几个串联的电解电容来对应高母线电压。 3 开关频率。频率值是由给定的电感值和电网要求预先确定的。如第二部分提到的,70 Hz是同时能满足效率和EMI要求的方案。

这些通过各种方法确认参数的初始值会通过仿真进行验证。用于确定初始值的方法包括:标准容感设计计算、借鉴现有设计、历史文献和图纸。利用深入分析这些方法,可以对参数进行有根据的猜测,我们将在后面的仿真结果中再次提到。

开始仿真

在这个部分中,我们将介绍为本次设计建立的仿真模型(次模型),并重点解释模型特点以及被忽略的内容。此外,还有针对不是基础或必要的模型所采取的措施。最后是一份总结表。

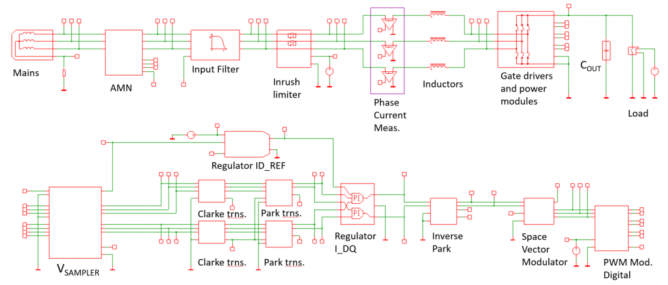

图1显示了在SIMetrix中的仿真模型,包括功率部分(上)和PWM部分(下)。后续会带来有关算法的内容。

PWM调制回路基于一个典型的空间矢量脉宽调制算法(SVPWM),能够简化控制回路并使其通过PI调节器寻址。我们使用了测量出的主相电压作为控制器输入来简化模型,而在实际的硬件系统里,我们需要在数字域中使用锁相环来测量瞬时电源参考电压。  图1. PFC部分的SIMetrix模型

母线和母线网络模型

电源模型由3条可配置的母线组成,能产生相位差为120°的50/60 Hz正弦曲线。初始相位可以更改,对于验证输入的浪涌电流保护回路很有帮助。为了方便考虑,大部分仿真模型中的负载都为阻性负载。

作为仿真的一部分,我们需要基本的、针对输入滤波的差模传导干扰(CE)的验证,可以在电源和滤波器之间插入人工电源网络(AMN,Artificial Mains Network)或阻抗稳定网络(LISN,Line Impedance Stabilization Network,根据CISPR22)。对于这块内容,我们不在本系列进行讨论。电网的模型也包括了影响控制的交流电网阻抗,因此加入仿真可以提高仿真的精确度。

输入滤波

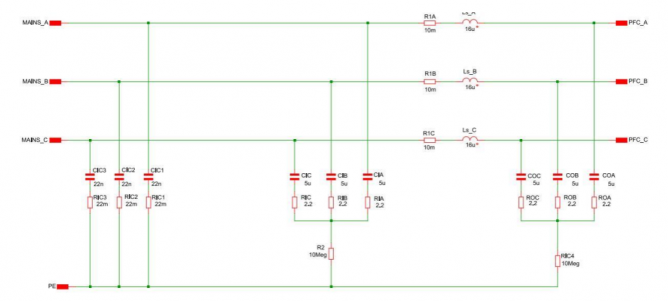

输入滤波是变换器的第一个部分,这次仿真我们不会做任何输入滤波模型的设计,所以采用了一个简化的模型(图2) 。如第二部分所提到的,那是一个现成的模型。

在这次的仿真中加入滤波器件带来了两个好处。第一,滤波器的输出阻抗是PFC控制回路的一部分,没有它我们很难得到一个可靠的PFC回路。在设计阶段,不考虑EMI滤波终究会给你的产品带来麻烦。

第二,为了得到一个更精确的效率和热管理的模拟,我们也将了滤波器的功率损失加入仿真。再次强调本次仿真的其中一个目标是为了验证我们的控制方案,以及会对最终产品性能有影响的器件。  图2. 输入滤波回路模型

浪涌电流保护

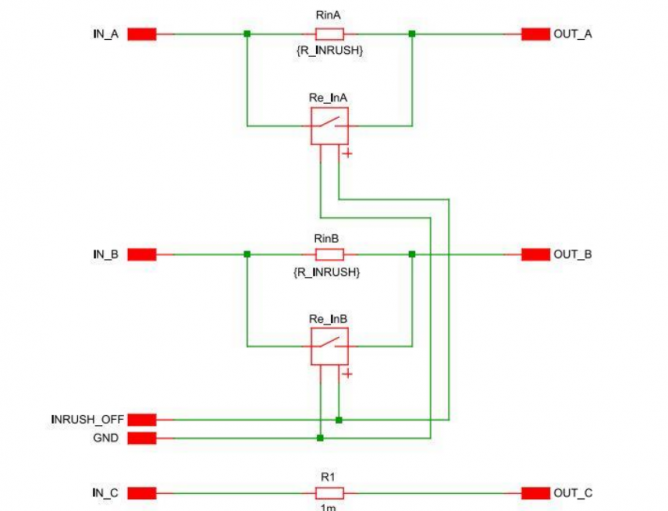

浪涌电流保护是EV充电系统中关键的一环,我们也需要为这一环做好仿真。该模型的实现并不复杂,典型的三相系统,其中两相由电阻和继电器并联构成,如图3。由于系统并不涉及到中性线,所以不必在第三相上增加电阻。(图1中的电阻R代表了连接产生的等效电阻。)

图3. 浪涌电流保护模型

一般来说,浪涌电流的仿真能够验证由电阻产生的最大能量耗散,从而帮助选择正确的元器件。

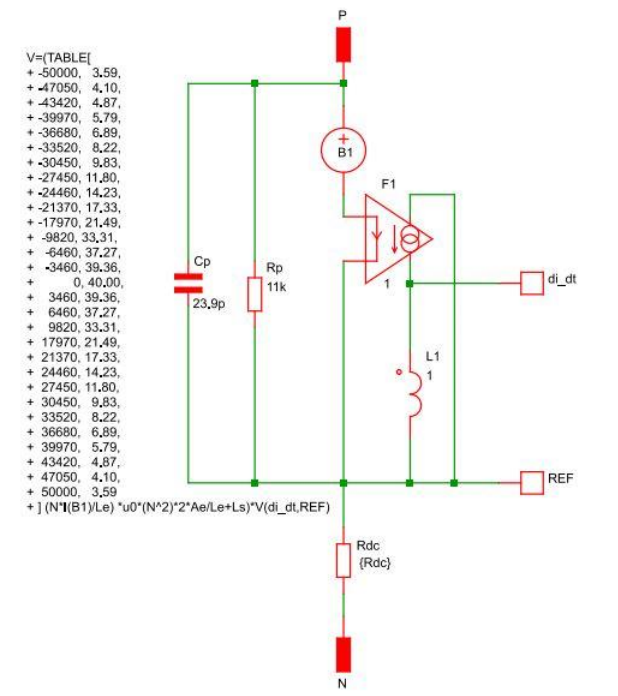

PFC电感模型

SPICE仿真软件能提供自带的电感模型,但较为简单且无法体现功率系统里电感的重要特性,比如自饱和和自谐振效应。图4中我们建立的模型则包含了这一些重要部分。电感饱和效应参考查找表,提供了相对磁感率(μr)和磁场强度(H)的关系。绕组损耗由一颗串联电阻体现。图4说明了更多有关这些元素在模型中的细节。

图4. 带饱和和自谐振效应的电感模型。 饱和效应(感值随着不同工作电流变化)的建模是根据查找表和磁性设计标准公式:(1) L = μ0 μr ( Ae/Le) N²,(2) H = (N × I)/Le ,(3) 查找表μr = f(H),(4) VL = L × dI/dt,B1为电感电压。L和dI/dt分别由(1)号公式和(4)号公式根据测试电感L1 (1H)推导得到。F1是一个电流驱动的电流源,1:1匝数比,输出等于电感模型测量值。因为L1 = 1H,所以dI/dt = V (dI_dt-REF) 。F1对电感模型没有任何影响,仅在计算每个点的VL、PFC的系统中,用于推导dI/dt。L (B1、F1和L1)、Cp和Rp模拟了电感的自谐振特性。

功率部分模型

功率部分是整个功率变换的重点,也是仿真模型的关键。它包含了3个半桥SiC模块和栅极驱动。驱动系统对整体性能的影响相当显著(对基于SiC的系统影响更大),所以我们强烈建议将其加入整体仿真,哪怕只囊括部分。然而目前的问题是已有的栅极驱动器的模型为了适应更多常见往往设计得较为复杂。一般而言,对系统级的模拟,或者说对本次项目的模拟,一个简化的驱动模型就已经足够了。

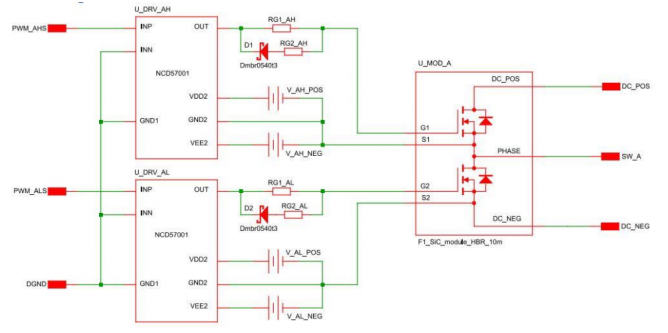

尽管驱动的参数表里不会详细的体现I-V关系,但我们可以通过使用特定几个点对应的驱动输出参数(最大输出/吸收电流)和上升下降时间来得到一个输出特性的近似值,从而提高了仿真的精确性和一个可接受的计算时间。我们使用这种方法来模拟栅极驱动器NCD57000。(图5)

图5. A相的功率部分模型

功率模块

为功率模块中的SiC MOSFET建模,显而易见地是整体仿真的关键步骤。如同栅极驱动器,也有具有相当详细的SiC MOSFET的模型存在,这些通常用于设备特性描述和提取任何工作条件下的设备参数。这些模型扩展了数据表中往往在特点工作点下所展示的信 息[3]。

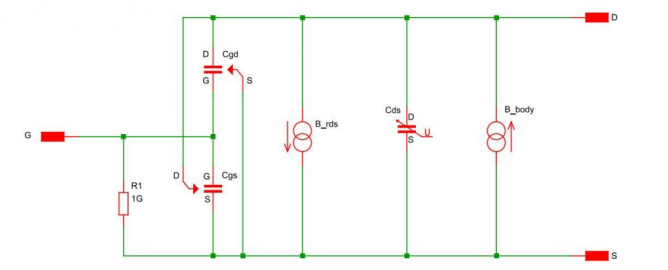

然而,在我们的仿真模型中,我们需要6个不同的开关器件,而这些模型会让仿真变得相当缓慢。趋同问题也经常出现。所以在这种情况下,我们可以采用一种实用的方法:创建一个简化的,包含对整体系统有巨大影响的主要元素和特性的模型。(图6)

图6. 简化后的MOSFET模型

上图的模型能够体现以下几个SiC MOSFET的关键参数:3个主要的寄生电容,RDS(ON)和体二极管的压降VF。这些不是单个数值,而是不同工作情况下的特征曲线。

需要注意的是寄生电容的参数随着VDS的变化而变化。VDS的特性表往往会在产品手册中提供,但需要一些推导计算。我们用下方程来计算模型数值,3个寄生参数分别以CISS,COSS和CRSS表示。

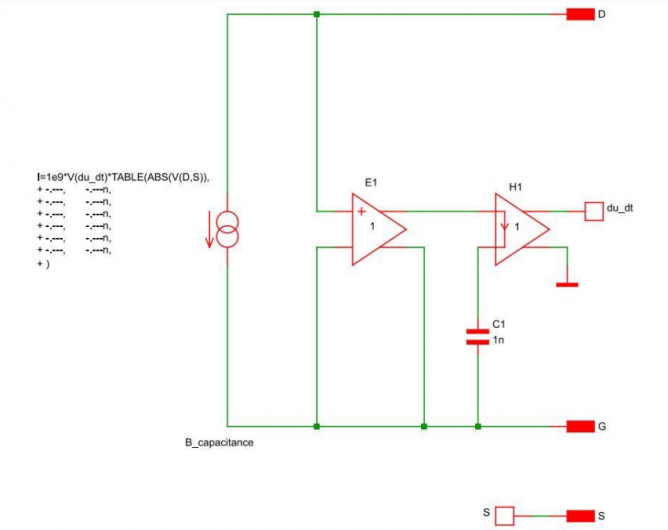

图7表示本次项目中使用的仿真模型,容值的非线性曲线基于参数对照表。

图7. Cgd的模型。Cgs和Cds的模型相同,但容值不同。

SIC MOSFET的RDS(ON)很大程度上取决于栅极电压VGS,其特性包含于“B_rds”的模型中。虽然VGS对RDS(ON)的影响很大,但它也会一定程度上随瞬时ID和VDS变化,不过在本次仿真中,不考虑这个特性带来的影响。

体二极管的VF-电流特性可以简单地建立一个电压电流查找表来建模。流过二极管的电流和体二极管地压降VF有关。体二极管的VF特性也许并不是对所有的应用都有用,但在三相PFC中,体二极管在整流电路中是相当重要的,而且其VF-电流特性会显著地影响开关死区的设置,所以在整个系统中非常重要。二极管的反向恢复特性在本次仿真中不被考虑。

需要强调的是基本的SiC MOSFET模型不包括PIN脚产生的寄生电感和电阻。所以添加一个内置的电阻能够更好地再现开关特性(dV/dt),从而选择或优化栅极电阻。其次,为了准确再现工作期间的电压尖峰,强烈建议对寄生电感进行建模,但对系统级别的验证来说没有那么关键,而且我们可以在实际操作的时候通过调整栅极电阻来优化开关特性。

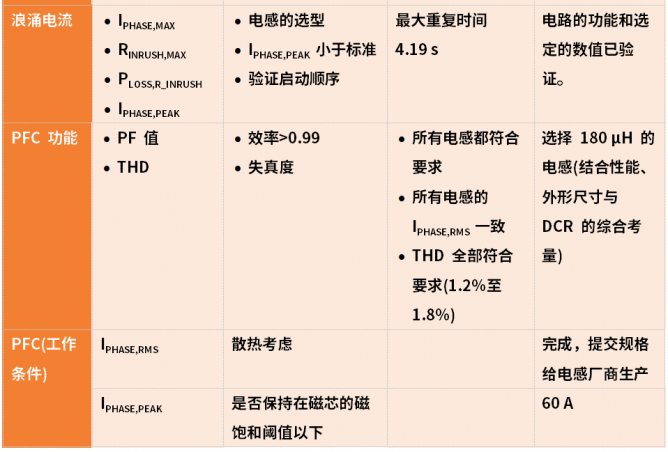

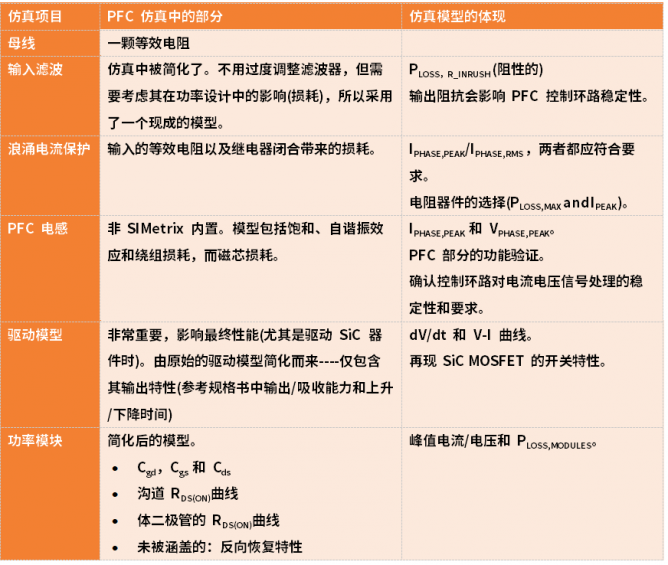

表一总结了仿真模型的内容以及每个部分仿真的输出。最终实际结果应当满足仿真结果,并且能解决我们预想的设计问题。  表1. 仿真模型总结:仿真包含的部分以及在仿真模型中的体现

仿真结果

在完成了建立仿真模型这项费时费力的任务后,我们快进到有意思的部分——使用并评估结论。

为了解决我们的问题,基于图2总结的变量,我们进行了一系列的仿真。在以下内容中,我们将展示得到的结果、我们对这些结果的观察以及基于这些结果的设计决策。

为了清晰起见,本章节末尾的表3总结了所有这些解释和说明。

PFC部分的效率

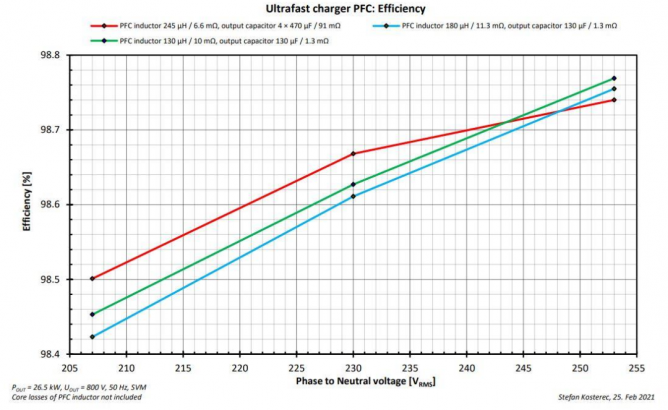

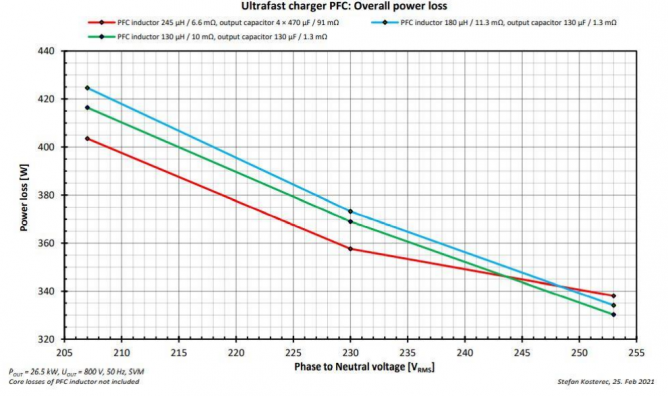

系统效率对整体仿真的结果相当关键。图8,图9和图10体现了效率值和相关的损耗。如我们预想的,更高的输入电压会带来更高的整体效率,因为IPHASE降低(图8)。

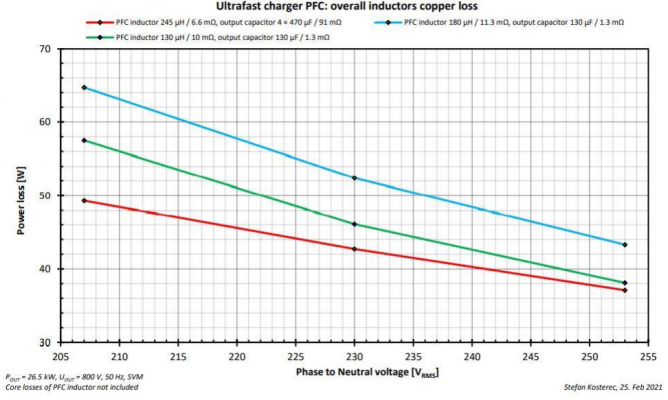

对于不同电感带来的结果,可以看到更高的感值可能会带来更高的效率。然而,有许多其它的器件会影响结果。它展示了仿真带来的好处,因为效率计算和不同工作节点时器件考量是非常繁琐的。图10提供了绕组损耗的细节;不同感值带来的绕组损耗差异比系统损耗差异小。  图8. PFC部分的效率和输入电压值、感值和输出容值的关系  图9. PFC部分的损耗和输入电压值、感值和输出容值的关系  图10. PFC部分的电感损耗和输入电压值、感值和输出容值的关系

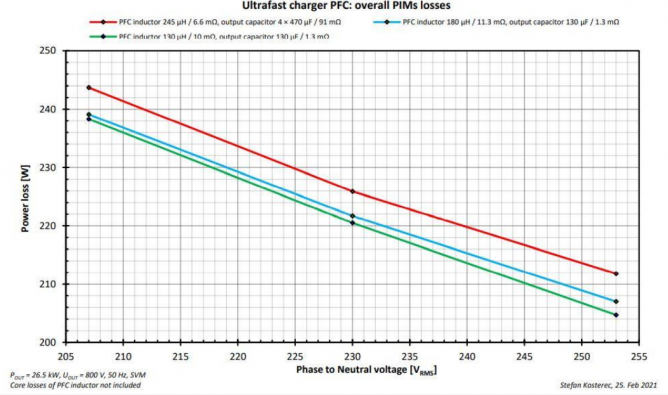

有关功率模块的损耗,仿真带来了有趣的信息(图11)。模块的损耗仅和感值相关。原因应该是更低的感值会带来更大的纹波电流,纹波电流越大,导通电流越低,所以开关损耗也降低了。  图11. PIM模块的整体损耗和输入电压值、感值和输出容值的关系

然而,功率模块和感值没有直接联系,因为调节的过程和PWM等也造成了影响。基于实际模型的仿真有助于预测结论即使无法直接确定实际关系。

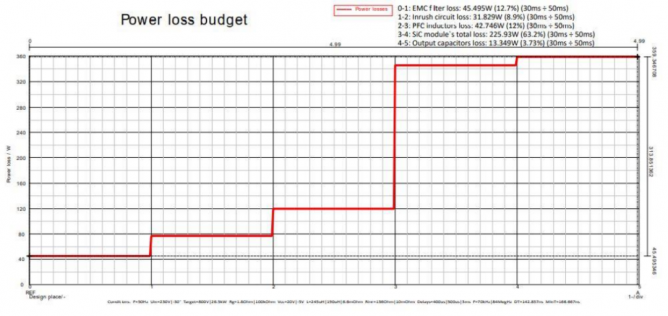

最有趣的发现是模型中多个元素(器件)造成的损耗分布(图12)。这个分布图能够帮我们搞清楚损耗的来源以及哪些部分需要关注从而提高效率。本次设计中,我们证明了在各种情况下系统效率都会大于98%,所以有关效率,没有什么问题。有了这些结果,我们可以选择最能满足其余系统需求的解决方案。  图12. 损耗的示意图。仿真的主要条件是VIN=230 V,POUT=26.5 kW,VOUT=800 V,感值容值为245 μH、4×470 μF。仿真的时间为50ms。能量损耗计算时,时间设置基本考虑30ms至50ms (用“30ms % 50ms”表示),以保证系统运行在稳定阶段。

浪涌电流仿真

浪涌电流控制仿真的主要目的是为了确认尖峰和电流有效值,以及在启动时由限流电阻带来的损耗。这项仿真能够帮助我们去验证限流电阻的选型。

一般来说,启动时的峰值相电流(100 μs以内)被限制在额定值的数倍。同样的,最大的相电流有效值也可以通过设置一个重复启动前的等待周期(几秒钟)来限制。

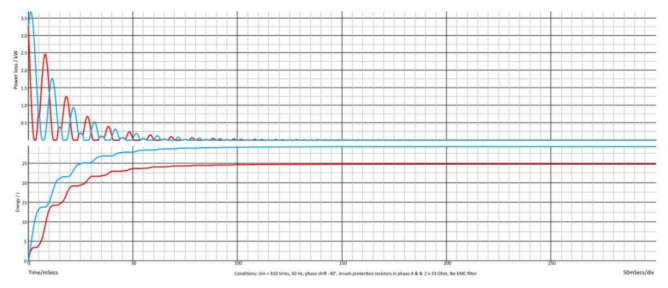

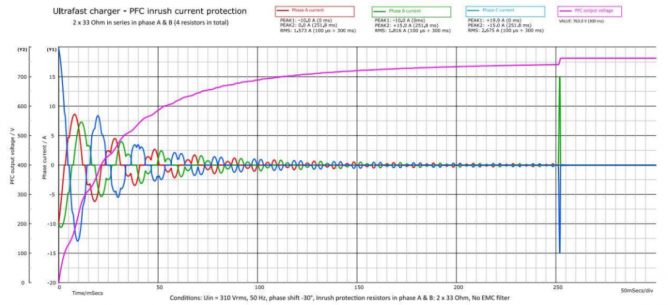

图13和图14展示了我们的系统在最差情况下的结果:母线相-零电压为310 Vrms,A相从0点偏移了-30°,450 μF的输出电容完全被耗尽。仿真告诉我们重复启动应该设置一个4.19秒的冷却时间以确保7 W的损耗要求(抗浪涌电阻的功耗)。然而,一般来说充电系统不会在短时间内重复启动(几秒内)。

图13. 浪涌电流保护。最差情况下,启动时功率损耗(顶部)和能量耗散(底部)波形,浪涌保护时COUT=450 μF,VIN=310 Vac。浪涌保护由每相2个33Ω电阻串联组成(共4个电阻)。红线:一颗抗浪涌电阻功率和能量(A相)。蓝线:一颗抗浪涌电阻功率和能量(B相)。A相和B相分别由24.81J和29.29J能量耗散,7W的功耗限制下的冷却时间分别是3.55秒和4.19秒。  图14. 浪涌电流保护。浪涌电流保护时A相和B相的输入电流以及PFC输出电压。与图13一样,与保护电流和COUT有关。

PFC参数

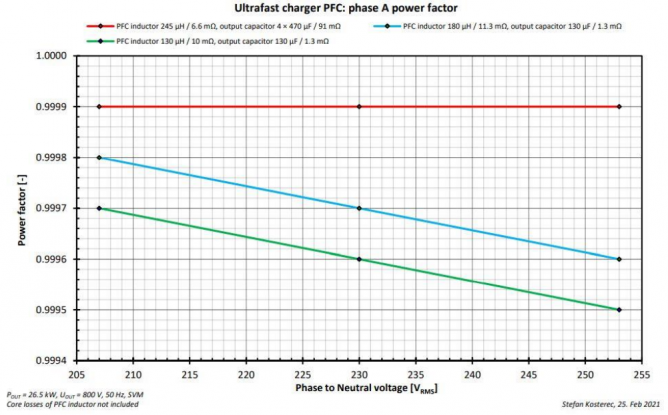

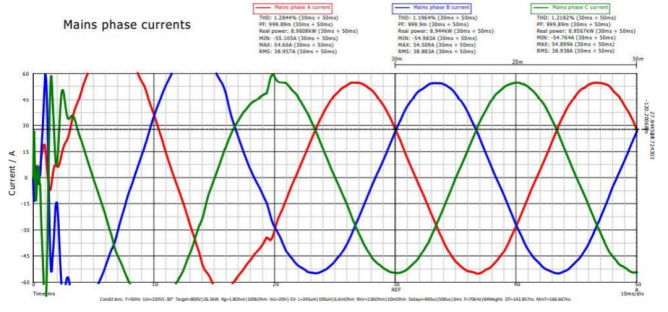

功率因数是一个关键的要求,EV快充规定要求功率因数满载下必须达到0.99。图15验证了所有设计都能满足功率因数要求,图16呈现了一个完美的正弦电流波形以及IPHASE-VINPHASE关系。

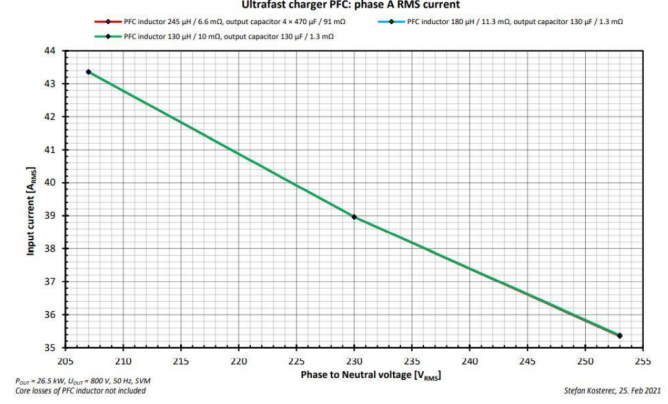

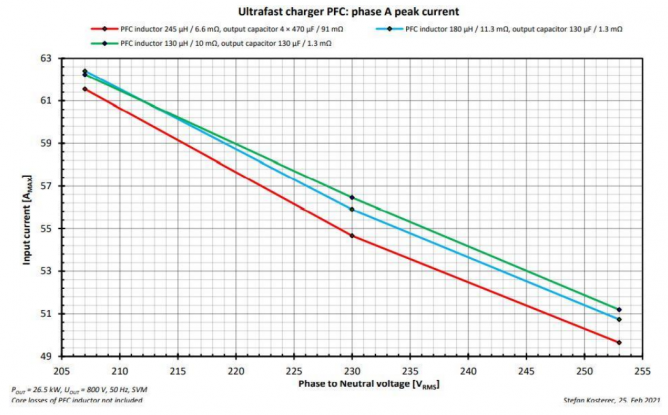

无论感值如何变化,IPHASE,RMS几乎保持不变(图17),与总体效率结果相吻合(图8),因为不同型号的电感之间的变化也非常小。在峰值电流上可以观察到稍大的变化(图18),但IPHASE,PEAK值对功率损失并不关键,因为IPHASE,RMS才是用于估计损失和效率的主要因素。

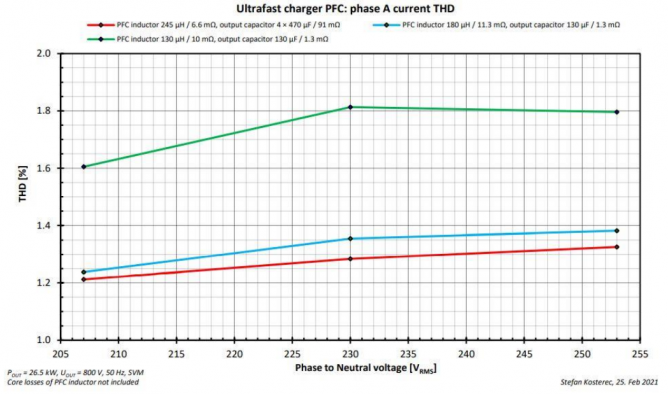

可以确定地是电流越大,系统损耗越大。总谐波失真(THD)结果也体现了这一点(图19)。  图15. 功率因数和输入电压值、感值和输出容值的关系。所有情况的功率因数均>0.99。  图16. 相电流曲线,PFC电感245 μH。PFC A相功率因数0.999,VIN=230 V。  图17. 输入电流有效值和输入电压值、感值和输出容值的关系。  图18. 输入电流峰值和输入电压值、感值和输出容值的关系。  图19. 输入电流总谐波失真(THD)和输入电压值、感值和输出容值的关系。

PFC电感工作条件

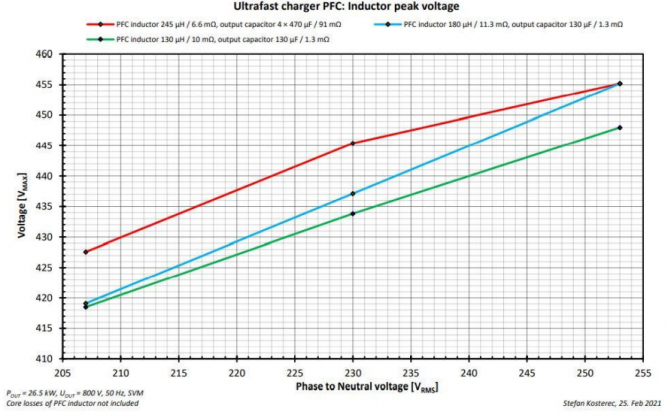

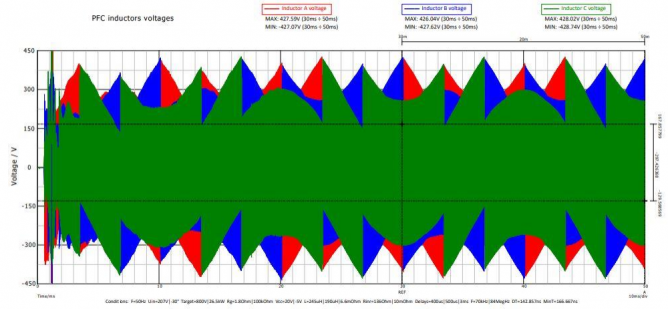

如表1提到的,彻底了解电感电流对设计性能优异的PFC电感很有帮助。设计或选择一个合适的电感,我们需要考虑以下4个关键的电流值,他们都可以通过仿真得到。

IPHASE,RMS,解决散热问题(图17) IPHASE,PEAK,计算磁芯的磁饱和度(图18) IRIPPLE,PEAK-PEAK,估算磁芯损耗(本次仿真不包括磁芯损耗,但建议另外计算) VPHASE,PEAK,定义绕组的绝缘等级

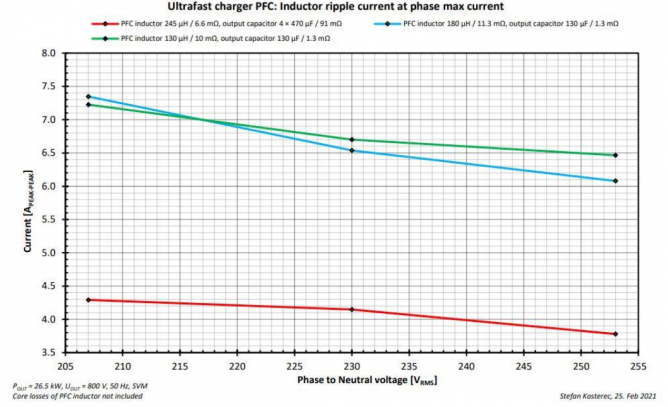

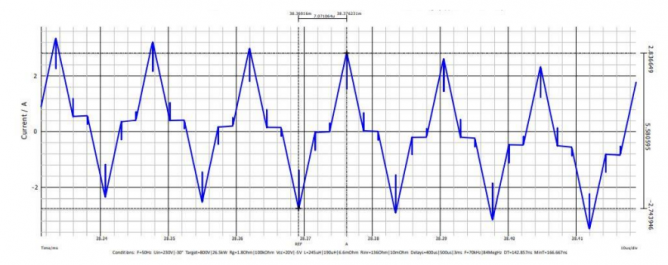

图20显示了在不同VPHASE-NEUTRAL电感纹波电流的峰-峰值。感值为245 μH时的纹波电流比130 μH的情况小40%。另一个细节是我们通过仿真知道了实际的IRIPPLE,PEAK-PEAK如何在在波形过零点和顶点达到最大和最小值的。图21和图22体现了这些差异。

我们还可以看到实际的纹波电流曲线和频率的形状在同一个点是有差别的。这样的情况在SVM里比较常见且并不会造成问题。(我们不会在本文对这一内容进行深入讨论,但它与CCM和DCM中的变换过程有关。)

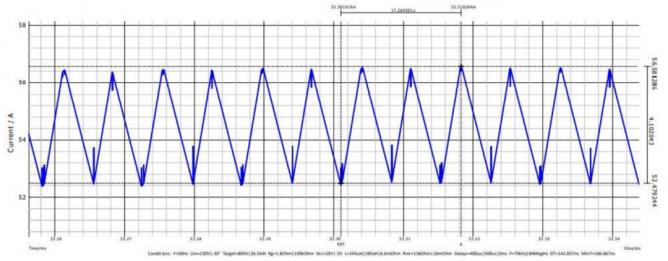

电感设计需要考虑纹波电流的最大峰-峰值。设计电感的另一个重要因素是电感的耐压值。图23和图24体现了这些数值。  图20. 电感纹波电流和和输入电压值、感值和输出容值的关系  图21. 峰值电流正弦波形时的电感电流细节。条件:B相,VIN=230 V,POUT=26.5 kW,LPFC=245 μH。波形参数:IPHASE,RMS=38.9 A,IPHASE,PEAK-PEAK=4.1 A。X轴:10 μs/div。  图22. 电流正弦波形过零点时的电感电流细节。条件:B相,VIN=230 V,POUT=26.5 kW,LPFC=245 μH。波形参数:IPHASE,RMS=38.9 A,IPHASE,PEAK-PEAK=5.58 A。X轴:10 μs/div。  图23. 峰值电感电压和输入电压值、感值和输出容值的关系。  图24. PFC电感电压包络仿真。典型采用SVPWM的系统波形。

母线和DC输出之间的电压

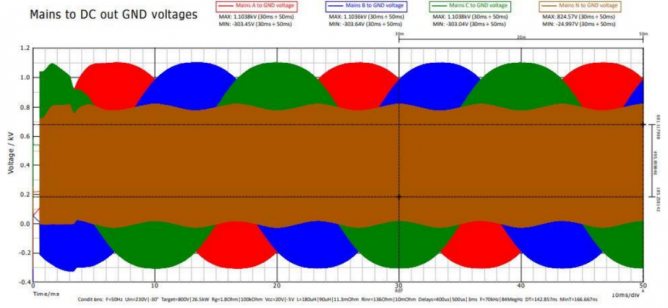

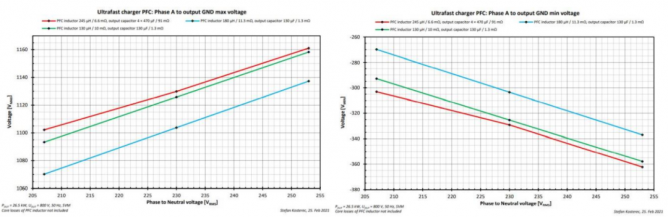

在三相PFC系统和逆变器中,相线、零线线(N)地线(PE)与转换器的直流负输出(-VDC)之间可能出现电压差,因为系统的前后部分没有进行电气隔离(在PFC部分)。所以在仿真和开发过程中必须要考虑这个可能性。

图25是输入和直流负输出(-VDC)的电压包络,以及零线或地线与直流负输出的压差。图26和图27表现了电压从-300 V提高至 1100 V的过程。我们需要至少在设计电感和PCB时考虑到这些电压等级。如此高的电压可能会造成PCB上器件和电感的隔离问题。除此之外,零线/地线与直流负输出之间的高压和dV/dt会带来不同性质的噪声,尤其是连入PFC输出的系统会特别容易受到共模噪声的影响。

之后的硬件测试和评估阶段,零线/地线和负输出电压之间的高电压可能需要额外小心和额外的安全措施。仿真在揭示必须解决的问题方面再次发挥了重要作用,帮助我们实现稳健的设计,也有利于今后的开发过程。

有趣的是,零线/地线到直流输出GND电压的包络被三倍的电网频率影响,调制深度与PFC电感的饱和度有关(图25)。这些现象受到PWM调制策略的影响,在我们的案例中,对应于在SVPWM系统中看到的包络。  图25. 相电压和零线/地线到DC输出地线的电压包络  (a) (b) 图26. A相到直流负输出(-VDC)的最大电压差(a)和最小电压差(b)和输入电压值、感值和输出容值的关系  (a) (b) 图27. 地线到直流负输出(-VDC)的最大电压差(a)和最小电压差(b)和输入电压值、感值和输出容值的关系

PFC输出电感

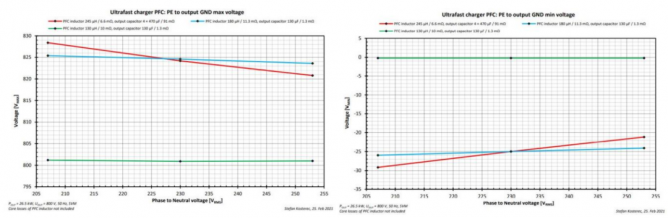

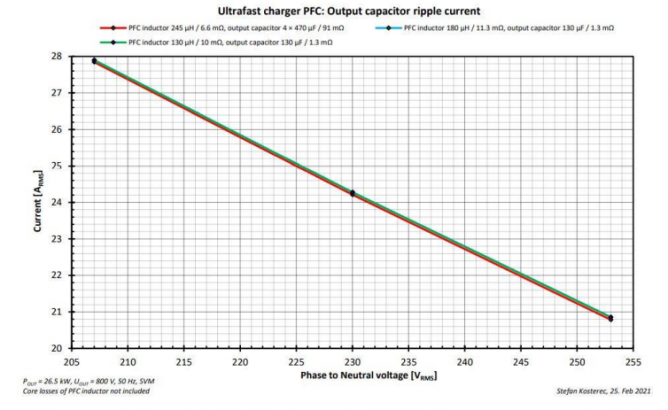

在功率因数校正之后,PFC系统的主要工作就是提高直流母线电压(boost dc-link voltage)并保持在参考值。直流母线电容作为boost电容,还需要有效地处理负载连接到输出端时产生的电流纹波。仿真能够帮助我们了解一旦实际硬件系统建立完成后这两个变量(直流母线电压以及纹波电流)将会如何变化。

图28告诉我们电容的输出电流不会随着电感或电容值的变化而急剧变化。另外,±10%的输入相电压VPHASE变化会带来约±15%的纹波电流变化(图29)。

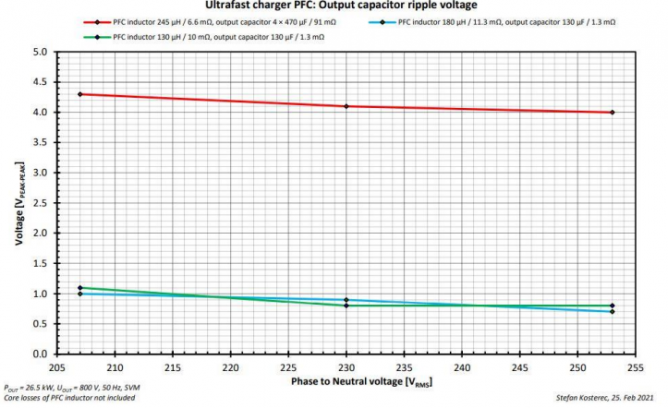

输出的交流电压分量(VPEAK-PEAK)与输入相电压VPHASE无关,但会被DC输出电容和寄生等效电阻(ESR)所影响。图30展现了4倍VPEAK-PEAK下的最差情况,4个470 μF电容并联。  图28. 输出电容电流ICAPACITOR,RMS和输入电压值、感值和输出容值的关系  图29. 典型的输出电感波形。条件:VIN=230 V,POUT=26.5 kW 结果:ICAPACITOR,PEAK-PEAK=58 A,ICAPACITOR,PEAK=25 A,ICAPACITOR,RMS=24.78 A。X轴:10 μs/div。  图30. 输出电容纹波电压输入电压值、感值和输出容值的关系

开关转换:开与关

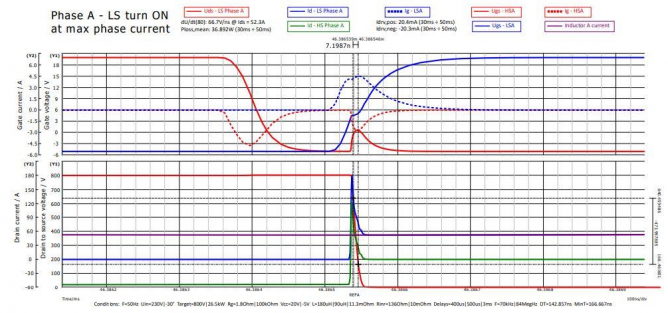

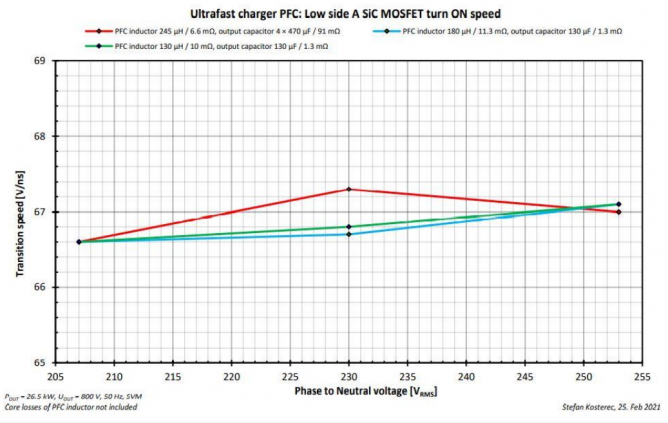

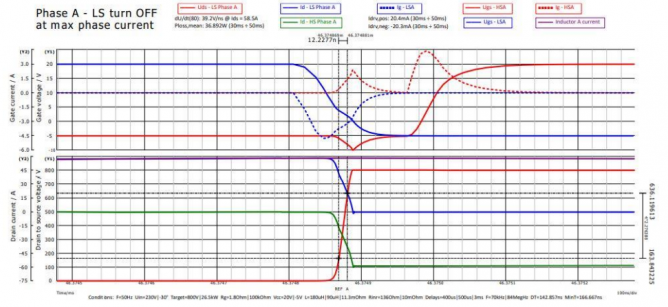

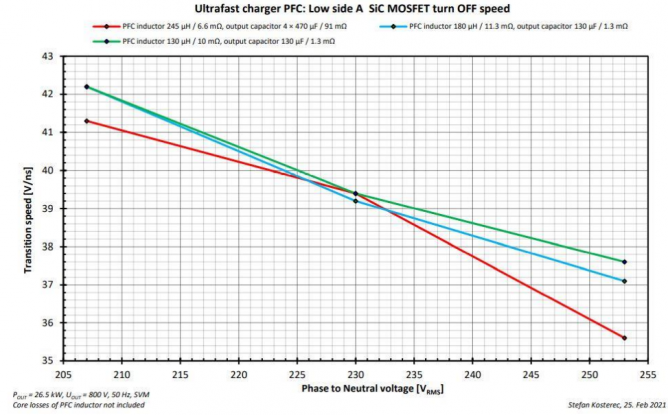

验证PFC部分的开关性能的一个关键参数是开关速度(图31),或者MOSFET的dV/dt。理论上来说,开关速度越快,损耗越低,效率越高。然而,仍然有其它因素限制开关速度。比如,开关管本身承受这种高梯度变换或EMI或其他快速开关产生的共模(CM)噪声的能力。

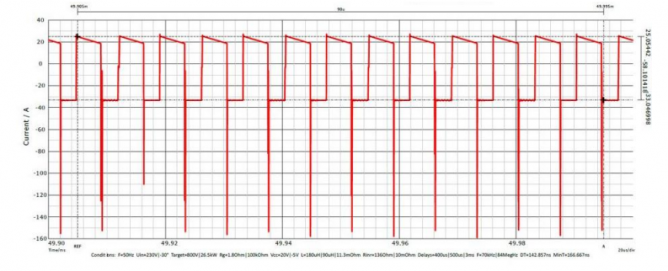

图31. PFC MOSFET的开启波形

图32显示在本模拟中给出的配置下,dV/dt值超过了66 V/ns,唯独宽禁带技术才能对应这样的高速开关。实际上,如此高的dV/dt仍然会有高风险(即使是SiC模块),寄生电感产生的超高过压尖峰可以轻易的超过器件的耐压上限。  图32. 低边A相SiC MOSFET开关速度和输入电压值、感值和输出容值的关系

调整栅极电阻是最简单的方法来减少dV/dt。更大的栅极电阻值能减少开关速度,同时减少整体设计的风险,但也会带来缺点,即少许的功率损失(因为开关速度没有那么快)。基于这项仿真的结论,我们决定做一个折中方案,换一颗阻值大一点的栅极电阻(1.8 Ω—>4.7 Ω)以确保MOS管导通时的dV/dt在25 V/ns左右。这将作为验证实际硬件板时的初始值。

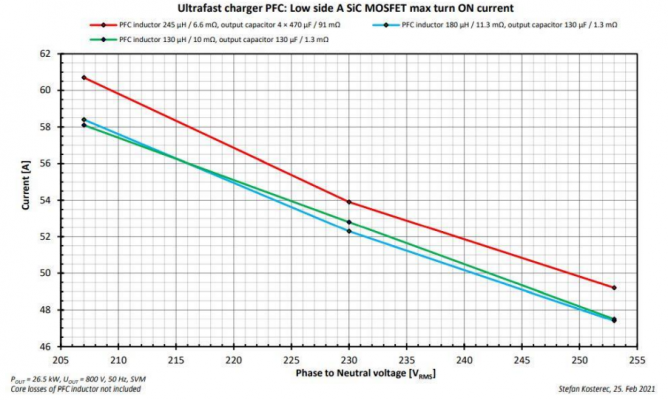

另一个影响开关效率的因素是开启电流。图33展示了仿真时得到的开启电流。不过,该系统的效率已经在以前得到验证,目前还没有预见对开启方式进行重大修改。  图33. 低边低边A相SiC MOSFET最大开启电流和输入电压值、感值和输出容值的关系

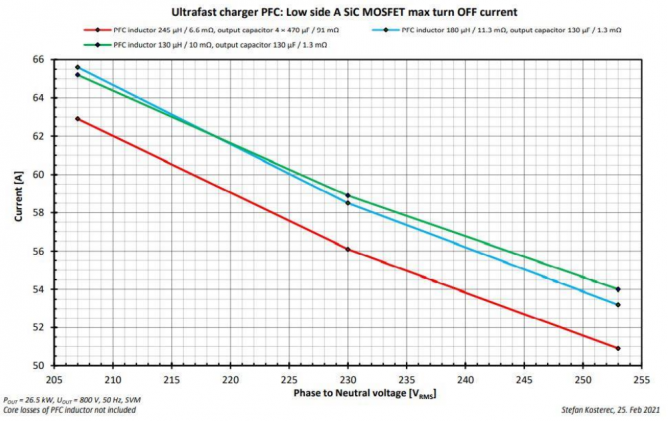

至于关断转换,我们也采取了类似的方法。图34、35和36显示了这些模拟的结果。使用100 kΩ吸收电阻时,关断过程也很快速(高达40 V/ns)。在测试板中,我们也会提高电阻以将关断dV/dt等级保持到25 V/ns左右。  图34. PFC MOSFET的关断波形  图35. 低边低边A相SiC MOSFET最大开启电流和输入电压值、感值和输出容值的关系  图36. 低边A相SiC MOSFET开关速度和输入电压值、感值和输出容值的关系

仿真结果和结论

其中一个仿真的最终目的是减少硬件的迭代次数并加速新产品量产过程。通过这篇文章,我们可以清晰地认识到在仿真和设计模型之前设定一个目标的重要性。仿真的结果将有助于回答我们的开放性问题,验证我们的假设,或者为系统的运行或优化揭开必要的修改。表3总结了上述模拟的结果。

|